# Voltage Level Shifter Using Modified Wilson Current Mirror

N. Minakhi, Priyanka Karmakar

**Abstract**-A Low Power Voltage Level Shifter is used as an intermediate between blocks and systems. This Voltage Level Shifter uses low-power to convert sub-threshold voltage level to above threshold voltage levels. This paper presents a Voltage Level Shifter which has an operating range from sub-threshold level to supply voltage. The Proposed Voltage Level Shifter uses a Modified Wilson Current Mirror and an Inverter. The circuit is able to convert a wide range of voltage levels to other levels. The circuit is designed in 180nm, 90nm and 45nm CMOS Technology in Cadence Virtuoso Simulator and simulation is done. The parameters such as power, delay, PDP and area is calculated. Propagation delay is decreased by 10% and power consumption by 12%.

Keywords- Current mirror, DELAY, PDP, Power Consumption, Power Dissipation, sub-threshold, Voltage level shifter,

## I. INTRODUCTION

Now-a-days, everyone wants a device which is easy to handle, have smaller size, uses low- power and speed is more. The factors which are mainly focused in designing a circuit are TAP (Time, Area and Power).

N.Minakhi is currently pursing master degree in VLSI &Embedded systems in Biju Patnaik University for Technology, <u>India. Email-</u> <u>minakhi.giftian@gmail.com</u>

Priyanka Karmakar , Faculty in BPUT, Dept.of ECE, India

Email- 90.priyanka.karmakar@gmail.com

It means a device should be have smaller area, uses low power and should produce output in time with less power dissipation and less propagation delay [9].During manufacturing of a device these factors are considered mainly. Area can be reduced by shrinking the size of transistors used in the circuit. And, power dissipation can be reduced by decreasing the supply voltage because power dissipation is square of power supply [1-2], [10]. So, by reducing supply power, propagation delay increases in the circuit which is a major disadvantage.[1]

In larger circuits, the whole circuit is divided into smaller parts and each part is assigned with individual supply [1-3]. Supply voltage can be applied to different blocks on the basis of output generation in the circuit. For example, if the output of a block in the circuit is time-critical means the block has to provide an output on time where no delay in output is considered those circuits are applied with high supply voltage and, parts of a circuit where delay in output can be accepted are applied with low supply. But, disadvantage is that the higher voltage parts sometimes does not identify changes due to low voltage parts. [2] Hence, Voltage Level Shifter is used. It plays a key role between blocks using different power supply for their operation.

Here, a Voltage Level Shifter is proposed which has less area, less delay and power dissipation is less. In the design of the proposed Voltage Level Shifter a Modified Wilson Current Mirror is used [1].

Current Mirror is a circuit which copies the current from the original active device to the other device.

# II. CONVENTIONAL VOLTAGE LEVEL SHIFTER [1]

In order to have a comparison between different Level Shifters and proposed Level Shifter.

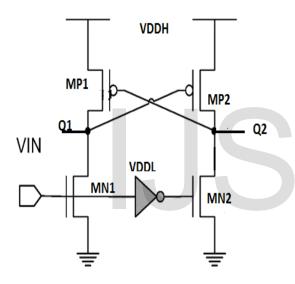

Fig.1 Schematic of Conventional Voltage Level Shifter [1]

When input signal is high, NMOS MN1 is on, making MN2 off. Node Q2 is pulled up to VDDH making MP2 and MP1 on and off respectively and node Q1 is pulled down. When input signal is low, NMOS MN1 and MN2 are off and on respectively. Then node Q1 is pulled up to VDDH making MP1 and MP2 ON and off respectively and Q2 is pulled down.

The major disadvantage is that there is a contention between NMOS and PMOS when NMOS tries to pull down the output

node . To eradicate this problem, NMOS transistor size needs to be increased which further increases delay in the circuit.

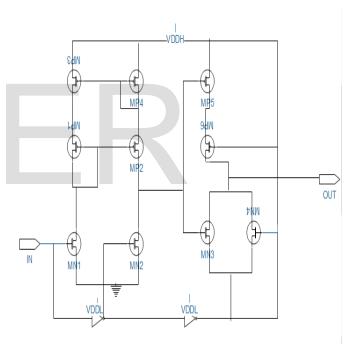

To solve the problem of contention between NMOS and PMOS which a raised in Conventional Voltage Level Shifter, Voltage Level Shifter using Modified Wilson Current Mirror with Hybrid Buffer is used. [2]

The whole circuit is further divided into three blocks- one blocks comprises of a Modified Wilson Current Mirror, second is the delay path and third one is the complementary OR gate. [1]

Fig.2 Schematic of Level Shifter using Modified Wilson Current Mirror Hybrid Buffer [2]

The operation of this Voltage Level Shifter is as follows, when input signal to the Level Shifter is high, MN1 and MN2 are on and off respectively. PMOS MP1 and MP2 are off and on respectively and the output of the Current Mirror is high. This output is fed to the Complementary OR gate and at node B the output is also high. So, MP5 is off and MP6 is also off giving output as high signal. The output of Complementary OR gate is fed to Inverter and we get high output from the inverter.

When input signal is low, MN1 is off and MN2 is on. And PMOS MP1 is on and MP2 is off and the output of Current Mirror is low. This output is fed to the Complementary OR gate and at node B the output is low. So, MP5 and MP6 are in on state making the output of Complementary OR as high. This output is given to the inverter and we get a low output signal from the inverter.

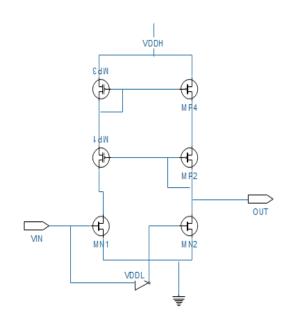

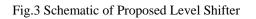

## III. PROPOSED STRUCTURE

The above structure is a Level Shifter having Modified Wilson Current Mirror, complementary OR gate and an inverter in the output side acts as a Level Shifter when difference between two voltages are small. To reduce power consumption complementary OR gate and inverter from the output side are removed. The proposed structure uses a Modified Wilson Current Mirror and an inverter between two NMOS. Since, the OR gate and inverter parts are removed the circuit becomes small. The operation is as follows, when input is high, MN1 and MN2 are on and off respectively. MP1 goes off and MP2 is on and output is taken as high. When input is low, MN1 is off and MN2 goes on making MP1 and MP2 on and off respectively.

## IV.SIMULATION RESULTS

The Proposed Level Shifter is simulated in different technologies, 180nm, 90nm and 45nm in Cadence Virtuoso Simulator in order to verify the performance in different technologies. Different types of level Shifters are also simulated keeping all the circuit parameters same as the parameters of the proposed circuit to have a fair comparison. Delay, power consumption and area of the circuits are compared.

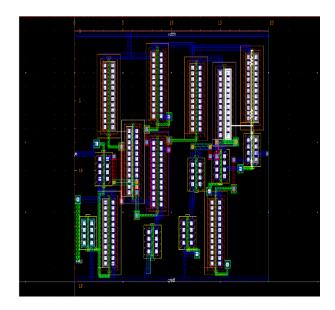

Fig.4 Layout of Level Shifter using Modified Wilson Current Mirror Hybrid Buffer [2]

(b)

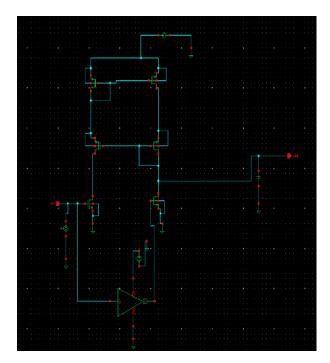

Fig.5 (a) Schematic of Proposed Level Shifter

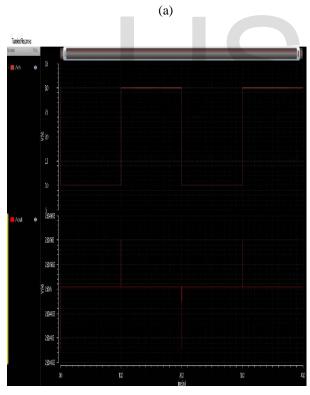

(b) Simulated Waveform

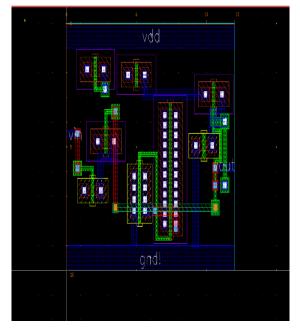

Fig.6 Layout of the Proposed Level Shifter

The power supply is changed to view the difference in power consumption. When VDH=3V and VDDL=1V is chosen , then VDDH=1V and VDDL=0.2V is applied and the delay and power consumption are compared.

# **TABLE-1**

COMPARATIONOFPROPAGATIONDELAYINDIFFERENTTECHNOLOGIES

# With VDDH=3V, VDDL=1V

| TYPES OF<br>LEVEL<br>SHIFTERS                                                      | 180nm<br>(in sec)         | 90nm<br>(in sec)           | 45nm<br>(in sec)            |

|------------------------------------------------------------------------------------|---------------------------|----------------------------|-----------------------------|

| CONVENTIONAL                                                                       | 5.29                      | 1.56*                      | 4.78*                       |

| LEVEL SHIFTER                                                                      | *10 <sup>-9</sup>         | 10 <sup>-11</sup>          | 10 <sup>-12</sup>           |

| LEVEL SHIFTER<br>USING<br>MODIFIED<br>WILSON<br>CURRENT<br>MIRROR<br>HYBRID BUFFER | 3.22*<br>10 <sup>-9</sup> | 1.37*<br>10 <sup>-11</sup> | 1.132*<br>10 <sup>-11</sup> |

| PROPOSED                                                                           | 1.56                      | 5.68*                      | 4.49*                       |

| LEVEL SHIFTER                                                                      | *10 <sup>-9</sup>         | 10 <sup>-12</sup>          | 10 <sup>-12</sup>           |

# TABLE-2

| COMPARATION  | OF | POWER     |

|--------------|----|-----------|

| CONSUMPTION  | IN | DIFFERENT |

| TECHNOLOGIES |    |           |

With VDDH=3V, VDDL=1V

| TYPES OF LEVEL<br>SHIFTERS                                                      | 180nm<br>(in<br>Watts)     | 90nm<br>(in<br>Watts)      | 45(in<br>Watts<br>)      |

|---------------------------------------------------------------------------------|----------------------------|----------------------------|--------------------------|

| CONVENTIONAL                                                                    | 202*                       | 148*                       | 107*                     |

| LEVEL SHIFTER                                                                   | 10 <sup>-9</sup>           | 10 <sup>-9</sup>           | 10 <sup>-9</sup>         |

| LEVEL SHIFTER<br>USING MODIFIED<br>WILSON<br>CURRENT<br>MIRROR HYBRID<br>BUFFER | 529.2<br>*10 <sup>-6</sup> | 340.9*<br>10 <sup>-6</sup> | 246*<br>10 <sup>-9</sup> |

| PROPOSED LEVEL                                                                  | 188.3                      | 168*                       | 142*                     |

| SHIFTER                                                                         | *10 <sup>-9</sup>          | 10 <sup>-9</sup>           | 10 <sup>-9</sup>         |

### TABLE- 3

COMPARATIVE TABLE SHOWING PDP OF LEVEL SHIFTERS IN DIFFERENT TECHNOLOGIES

With VDDH=3V, VDDL=1V

| TYPES OF                                                                           | 180nm                      | 90nm                       | 45nm(i                     |

|------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|

| LEVEL                                                                              | (in                        | (in                        | n                          |

| SHIFTERS                                                                           | Joules)                    | Joules)                    | Joules)                    |

| CONVENTIONAL                                                                       | 1.06*                      | 2.30*                      | 5.10*                      |

| LEVEL SHIFTER                                                                      | 10 <sup>-15</sup>          | 10 <sup>-18</sup>          | 10 <sup>-19</sup>          |

| LEVEL SHIFTER<br>USING<br>MODIFIED<br>WILSON<br>CURRENT<br>MIRROR<br>HYBRID BUFFER | 1.70*<br>10 <sup>-12</sup> | 4.67*<br>10 <sup>-15</sup> | 2.79*<br>10 <sup>-18</sup> |

| PROPOSED                                                                           | 2.93*                      | 9.54*                      | 6.37*                      |

| LEVEL SHIFTER                                                                      | 10 <sup>-16</sup>          | 10 <sup>-19</sup>          | 10 <sup>-19</sup>          |

# **TABLE-4**

| COMPARATIONO | POWER |           |

|--------------|-------|-----------|

| CONSUMPTION  | IN    | DIFFERENT |

| TECHNOLOGIES |       |           |

With VDDH=1V, VDDL=0.2V

| TYPES OF                                                                           | 180nm                    | 90nm                     | 45nm                     |

|------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|

| LEVEL                                                                              | (in                      | (in                      | (in                      |

| SHIFTERS                                                                           | Watts)                   | Watts)                   | Watts)                   |

| CONVENTIONAL                                                                       | 178.8                    | 143.4                    | 103.6*                   |

| LEVEL SHIFTER                                                                      | *10 <sup>-9</sup>        | *10 <sup>-9</sup>        | 10 <sup>-9</sup>         |

| LEVEL SHIFTER<br>USING<br>MODIFIED<br>WILSON<br>CURRENT<br>MIRROR HYBRID<br>BUFFER | 488*<br>10 <sup>-6</sup> | 332*<br>10 <sup>-6</sup> | 192*<br>10 <sup>-9</sup> |

| PROPOSED                                                                           | 145.9                    | 126.7                    | 102.2*                   |

| LEVEL SHIFTER                                                                      | *10 <sup>-9</sup>        | *10 <sup>-9</sup>        | 10 <sup>-9</sup>         |

# TABLE-5

| COMPARAT | IONOF | PROPAGATION |

|----------|-------|-------------|

| DELAY    | IN    | DIFFERENT   |

| TECHNOLO | GIES  |             |

# With VDDH=1V, VDDL=0.2V

| TYPES OF<br>LEVEL<br>SHIFTERS                                                      | 180nm<br>(in<br>second<br>s) | 90nm<br>(in<br>second<br>s) | 45nm(in<br>seconds<br>)    |

|------------------------------------------------------------------------------------|------------------------------|-----------------------------|----------------------------|

| CONVENTIONAL                                                                       | 9.68*                        | 4.56                        | 2.30*                      |

| LEVEL SHIFTER                                                                      | 10 <sup>-9</sup>             | *10 <sup>-11</sup>          | 10 <sup>-11</sup>          |

| LEVEL SHIFTER<br>USING<br>MODIFIED<br>WILSON<br>CURRENT<br>MIRROR HYBRID<br>BUFFER | 8.80<br>*10 <sup>-9</sup>    | 5.67*<br>10 <sup>-11</sup>  | 3.70*<br>10 <sup>-11</sup> |

| PROPOSED                                                                           | 3.23                         | 1.20*                       | 5.79*                      |

| LEVEL SHIFTER                                                                      | *10 <sup>-9</sup>            | 10 <sup>-11</sup>           | 10 <sup>-11</sup>          |

# **TABLE-6**

# COMPARATION OF PDP IN DIFFERENT TECHNOLOGIES

### With VDDH=1V, VDDL=0.2V

| TYPES OF                                                                           | 180nm                      | 90nm                       | 45nm(i                     |

|------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|

| LEVEL                                                                              | (in                        | (in                        | n                          |

| SHIFTERS                                                                           | Joules)                    | Joules)                    | Joules)                    |

| CONVENTIONAL                                                                       | 1.73*                      | 6.53*                      | 2.38*                      |

| LEVEL SHIFTER                                                                      | 10 <sup>-15</sup>          | 10 <sup>-16</sup>          | 10 <sup>-17</sup>          |

| LEVEL SHIFTER<br>USING<br>MODIFIED<br>WILSON<br>CURRENT<br>MIRROR<br>HYBRID BUFFER | 4.29*<br>10 <sup>-11</sup> | 1.88*<br>10 <sup>-14</sup> | 7.10*<br>10 <sup>-18</sup> |

| PROPOSED                                                                           | $4.71^{*}$                 | $1.52^{*}$                 | 5.91*                      |

| LEVEL SHIFTER                                                                      | $10^{-16}$                 | $10^{-19}$                 | 10 <sup>-18</sup>          |

6 shows delay, power consumption and PDP of different level shifters at different technologies when VDDH=1V and VDDL=0.2V. And, Table 7 shows area of level shifters at different technologies.

## V. CONCLUSION

The above schematics are simulated in Cadence Virtuoso simulated at 180nm, 90nm and 45nm CMOS technology. The propagation delay, power consumption and PDP are verified. For VDDH=1v and VDDL=0.2v, the delay is reduced by 10%, power consumption is decreased by 12% in 45nm technology.

## TABLE-7

COMPARATION OF AREA OF LEVEL SHIFTERS USING LAYOUT IN DIFFERENT TECHNOLOGIES

| TYPES OF<br>LEVEL<br>SHIFTERS | 180nm              | 90nm              | 45nm              |

|-------------------------------|--------------------|-------------------|-------------------|

| LEVEL                         | 300um <sup>2</sup> | $120 \text{um}^2$ | 45um <sup>2</sup> |

| SHIFTER                       |                    |                   |                   |

| USING                         |                    |                   |                   |

| MODIFIED                      |                    |                   |                   |

| WILSON                        |                    |                   |                   |

| CURRENT                       |                    |                   |                   |

| MIRROR                        |                    |                   |                   |

| HYBRID                        |                    |                   |                   |

| BUFFER                        |                    |                   |                   |

| PROPOSED                      | $120 \text{um}^2$  | $20 \text{um}^2$  | $9 \text{um}^2$   |

| LEVEL                         |                    |                   | × •               |

| SHIFTER                       |                    |                   |                   |

Table1,2 and 3 summarizes delay, power consumption and PDP of different level shifters at different technologies when VDDH=3V and VDDL=1V. Table 4,5 and

# ACKNOWLEDGMENTS

Im grateful to my parents, friends and my teachers who took a lot of pain for my and helped me complete this work.

#### REFERENCES

[1]Shien-ChunLuo, *Member, IEEE*, Ching-Ji Huang, and Yuan-Hua Chu," A Wide-Range Level Shifter Using a ModifiedWilson Current Mirror Hybrid Buffer," IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 61, NO.6, JUNE 2014.

[2] AlaTalebzadeh and Mehdi Saberi," A Low-Power Wide-Range Voltage Level ShifterUsing a Modified Wilson Current Mirror," 2016 24th Iranian Conference on Electrical Engineering (ICEE).

[3] IkJoon Chang, Jae- joon Kim, Keejong Kim and Kaushik Roy, "Robust Level Converter for Sub threshold/Super-threshold Operation: 100 mV to 2.5 V", IEEE Transactions on Very Large Scale Integration(VLSI) Systems, Vol. 19, No. 8, pp.1429–1437, August 2011. [4] Sven Lütkemeier and Ulrich Rückert, "A Sub threshold to Above threshold level Shifter Comprising a Wilson Current Mirror", IEEETransactions on Circuits and Systems- II, Express Briefs, Vol. 57, No. 9,pp. 721–724, September 2010.

[5] Jun Zhou, Chao Wang, Xin Liu, Xin Zhang, and Minkyu Je, "An Ultra-Low Voltage Level Shifter Using Revised Wilson Current Mirror forFast and Energy-Efficient Wide-Range Voltage Conversion from Sub-Threshold to Supply Voltage", IEEE Transactions on Circuits andSystems-I, pp. 1-10, Regular Papers, 2015.

[6] T.-H. Chen, J. Chen, and L. T. Clark, "Sub threshold to above threshold level shifter design," *J. Low Power Electron.*, vol. 2, no. 2, pp. 251– 258,Aug. 2006.

[7] D. Blaauw and B. Zhai, "Energy efficient design for sub threshold supply voltage operation," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2006, pp. 4–32.

[8] A. Wang, B. H. Calhoun, and A. P. Chandrakasan, *Sub-Threshold Design for Ultra Low-Power Systems*. Secaucus, NJ: Springer-Verlag, 2006, ser. Integrated Circuits and Systems.

[9] Padmapriya Kesari,"A Novel Energy Efficient Transmission gate Voltage Level Shifter for multi VDD systems," International Journal of scientific research and management (IJSRM),Volume-3,Issue-3,Pages- 2263-2266,2015.

[10] Priti Gosatwar, Ujwala Ghodeswar," Design of Voltage Level Shifter for Multi supply Voltage Design," International Conference on Communication and Signal Processing, April 6-8, 2016, India.

[11] Sven Lütkemeier and Ulrich Rückert," A Subthreshold to Above-Threshold Level Shifter Comprising a Wilson Current Mirror," IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 57, NO. 9, SEPTEMBER 2010.

[12] A. Chavan and E. MacDonald, "Ultra low voltage level shifters to interface sub and super threshold reconfigurable logic cells," in *Proc. IEEE Aerosp. Conf.*, Mar. 2008, pp. 1–6.

[13] Yuji Osaki, *Student Member, IEEE*, Tetsuya Hirose, *Member, IEEE*, Nobutaka Kuroki, and Masahiro Numa, *Member, IEEE*, " A Low-Power Level Shifter With Logic Error Correction for Extremely Low-Voltage Digital CMOS LSIs," IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 47, NO. 7, JULY 2012.

[14] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, pp. 1433–1439, 1989.

[15] Y. Taur and T.H. Ning, *Fundamentals of Modern VLSI Devices* Cambridge, U.K.: Cambridge Univ. Press, 2002.